Programmation d’un SOC ARM¶

Résumé

Les processeurs ARM sont devenus les plus processeurs utilisés au monde dans les systèmes embarqués, que ce soit en contrôle-commande ou dans les smartphones.

Nous étudions ici l’architecture des processeurs ARM, ce qui fait leur succès puis comment utiliser les différents langage assembleur, ARM/THUMB, de ainsi que la programmation système associée aux SOC (System On Chip) ARM.

Introduction à ARM¶

Les architectures ARM¶

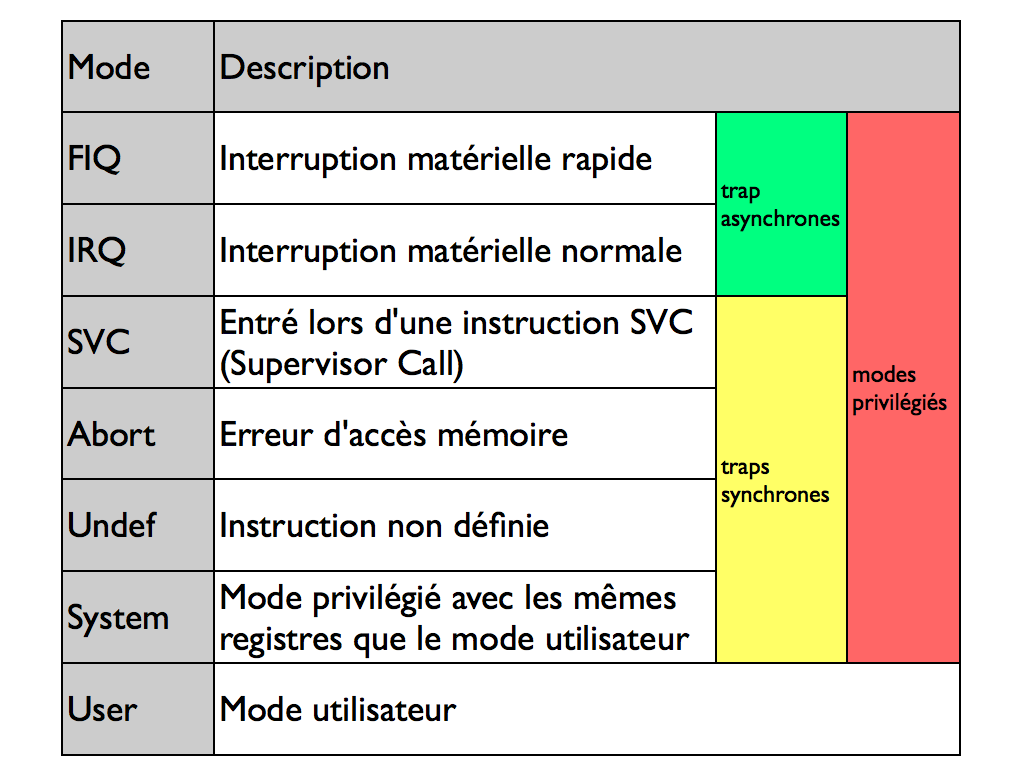

Modes de fonctionnement

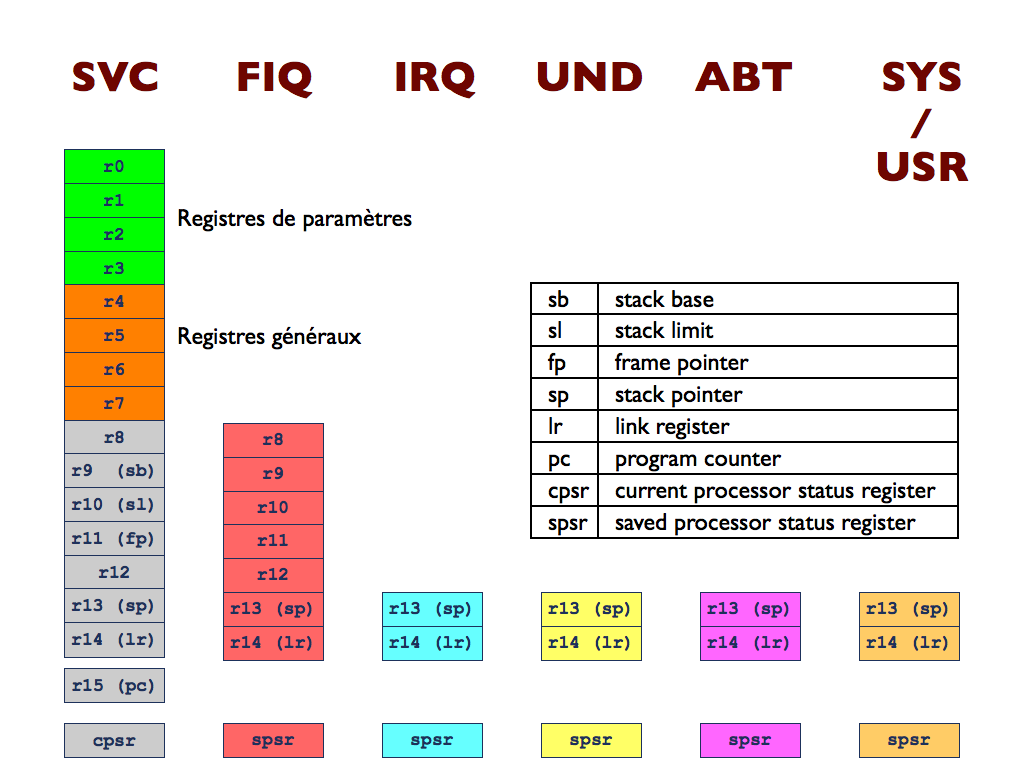

Les registres

Registre lors du retour des trappes

Accès aux registres

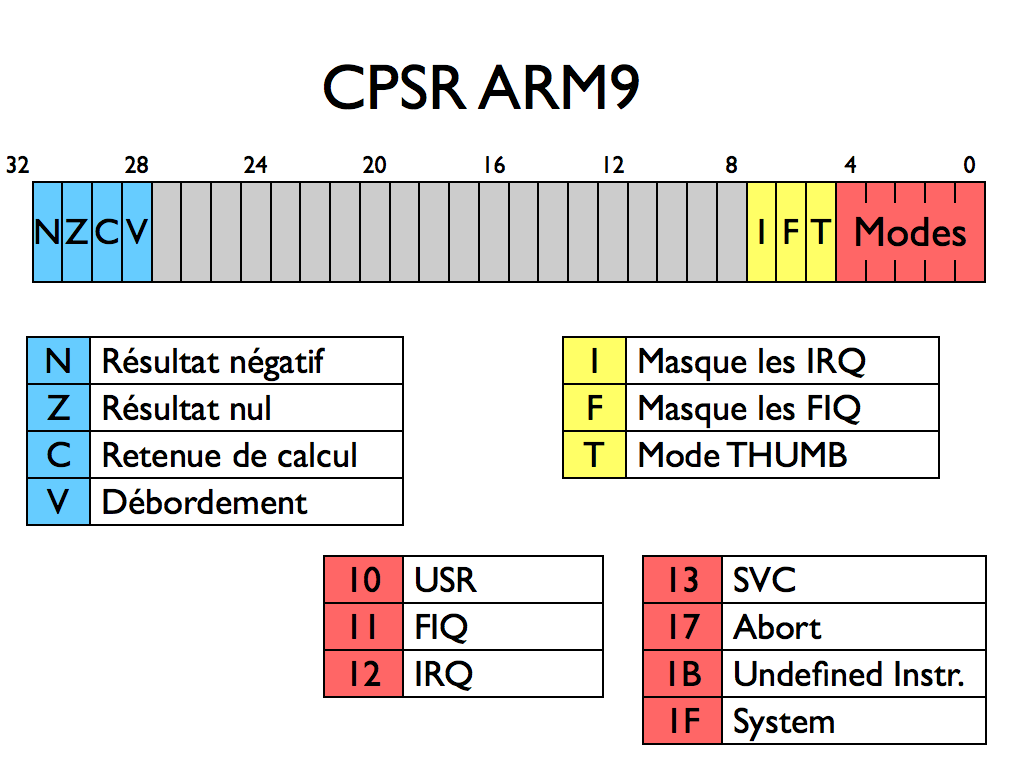

Le registre de status

Drapeaux de conditions (condition flags)

Le compteur de programme (R15)

Assembleur ARM¶

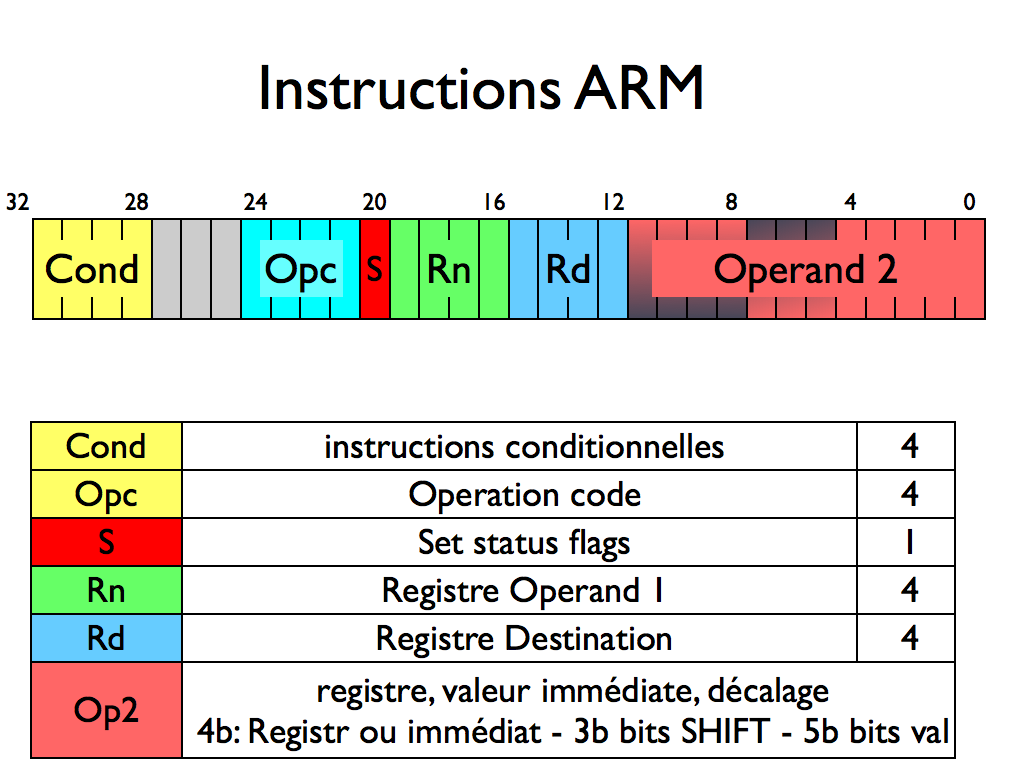

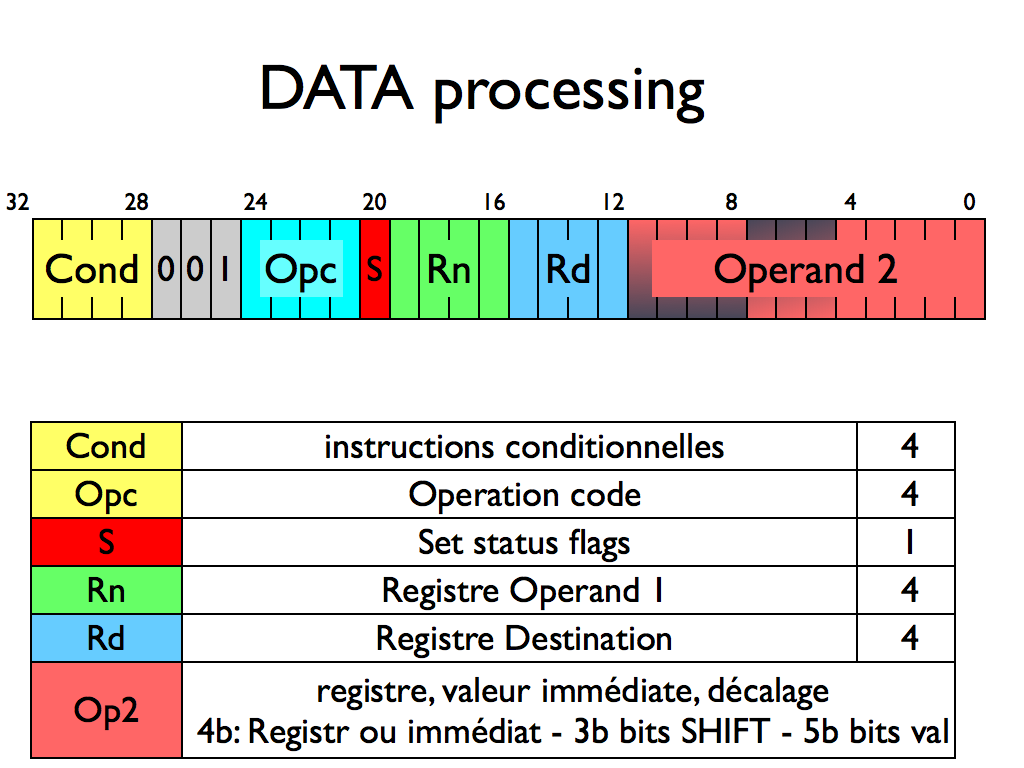

Les instructions ARM¶

mouvements de registre

Accès au registre de status CPSR et SPSR

opérations arithmétiques

Opérande immédiat

Arithmétique saturée

Multiplications et divisions

opérations logiques

Comparaisons

Exécution conditionnelle

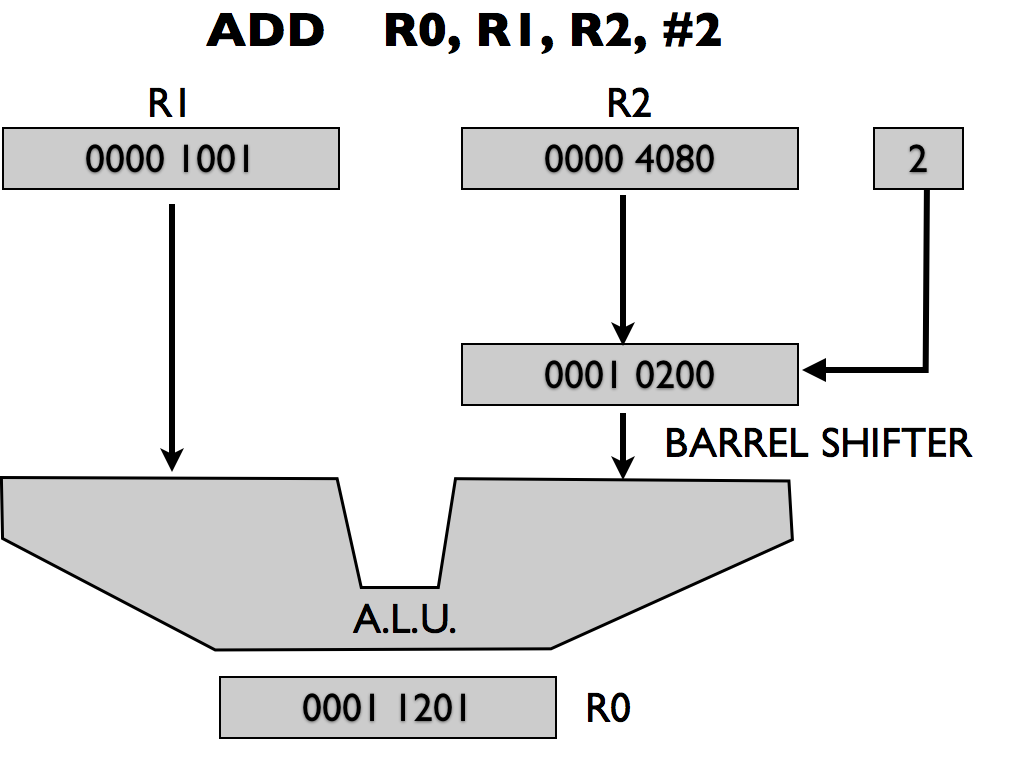

Barrel Shifter

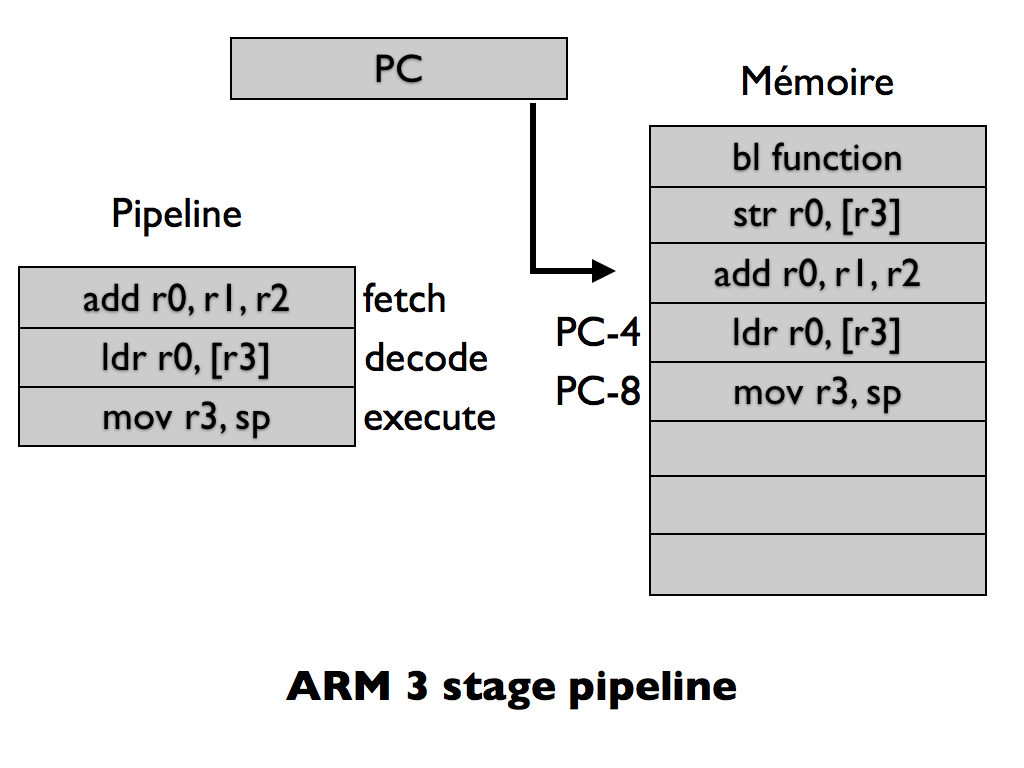

Pipeline

Branchements¶

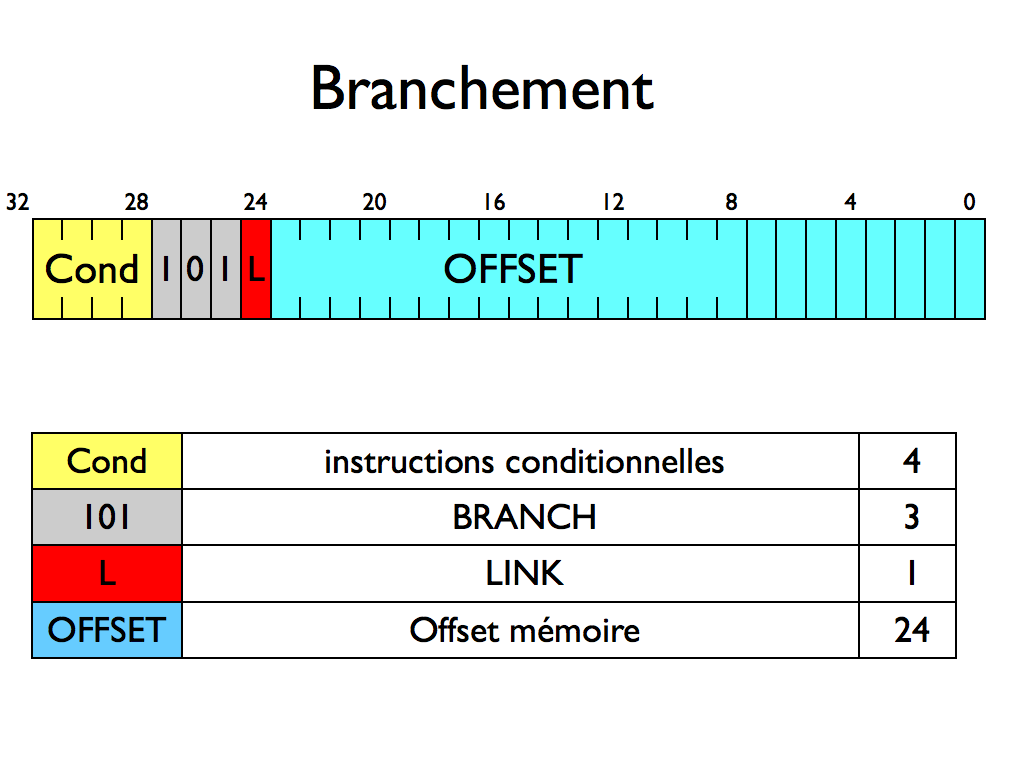

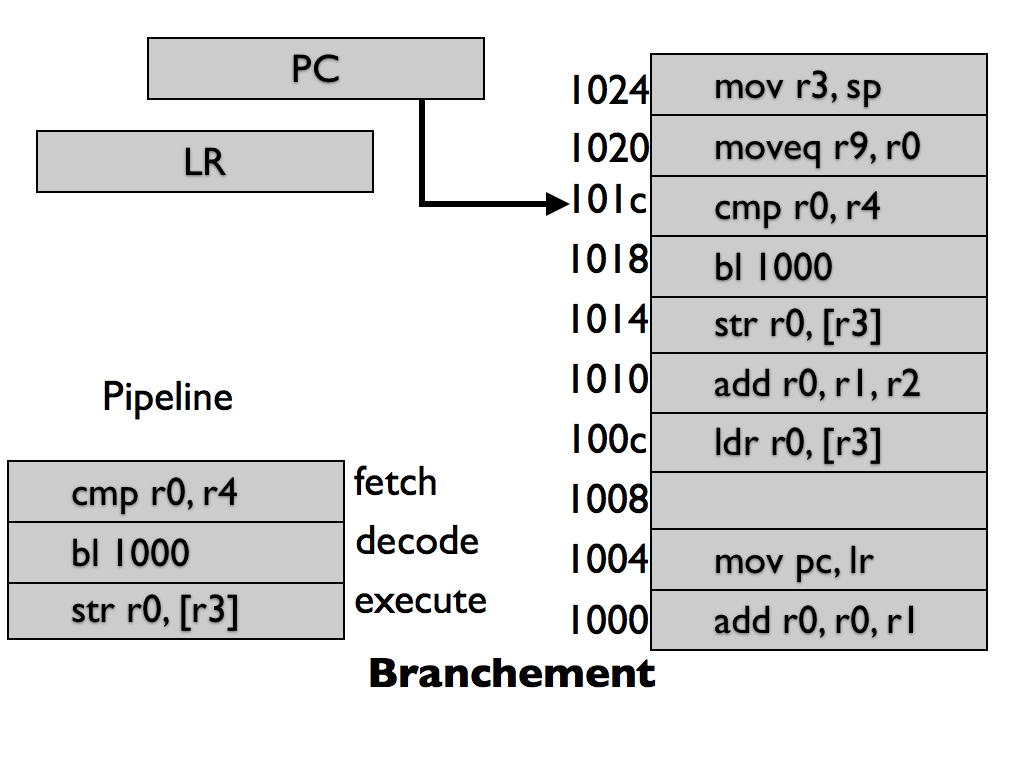

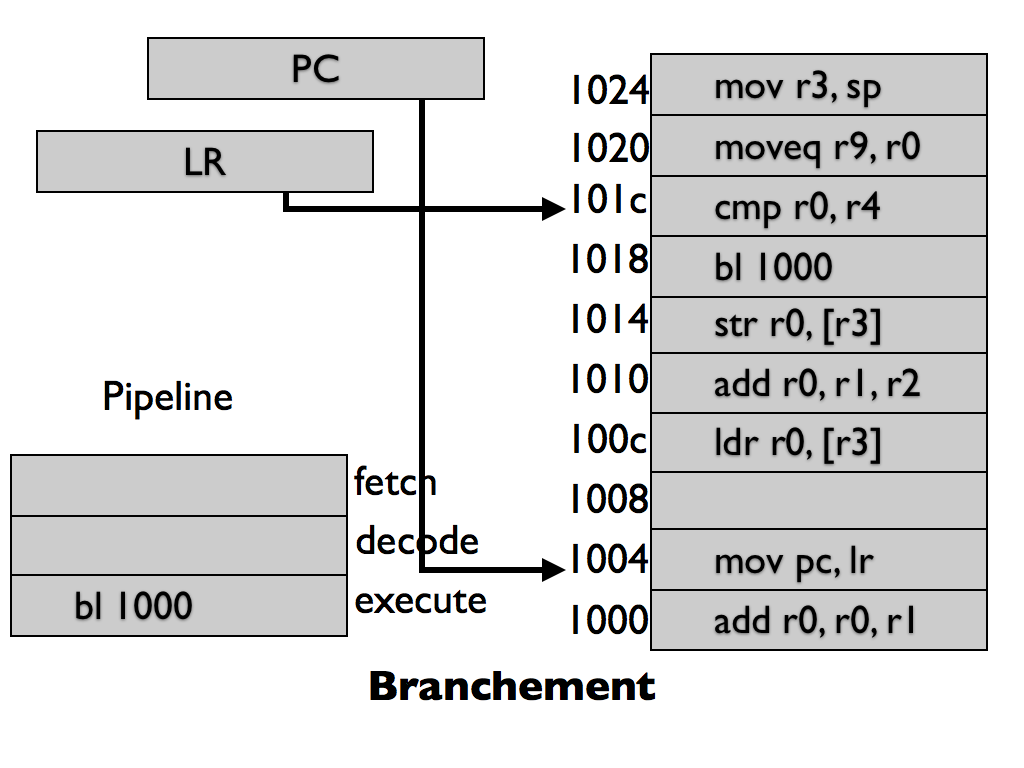

Instructions de branchement

Gestion des registres LR et SP

Retour d’appel

Passage en mode Thumb

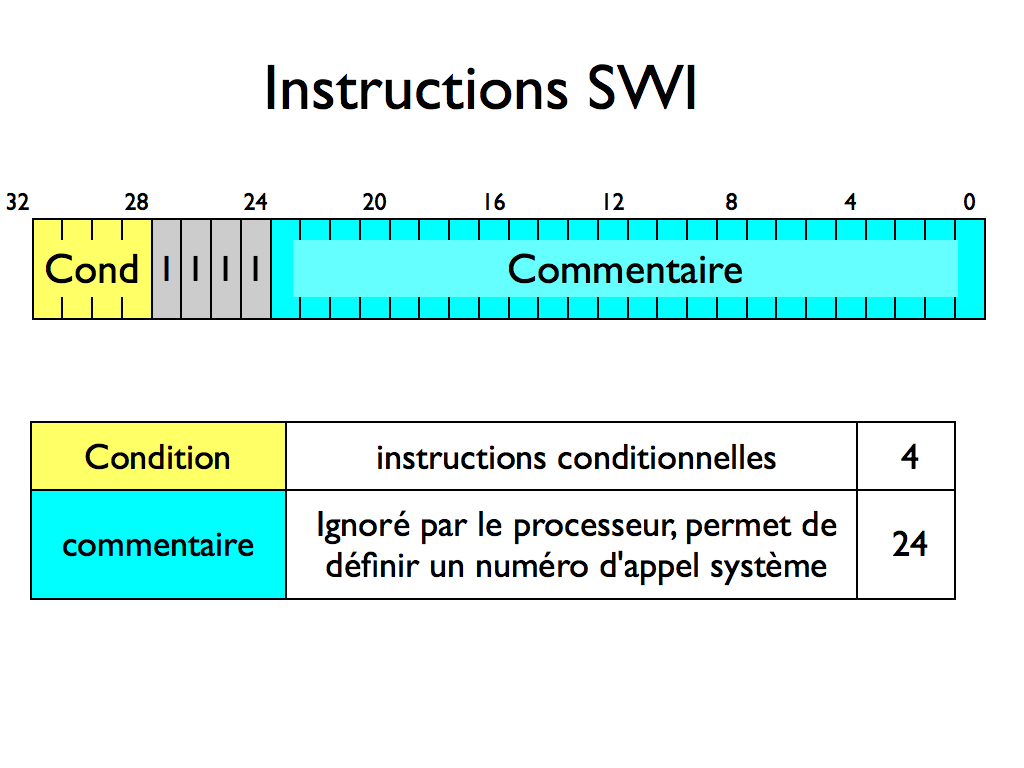

SWI: Software Interrupt

modification des registres lors d’une trappe

Accès au registre de status CPSR

Coprocesseurs¶

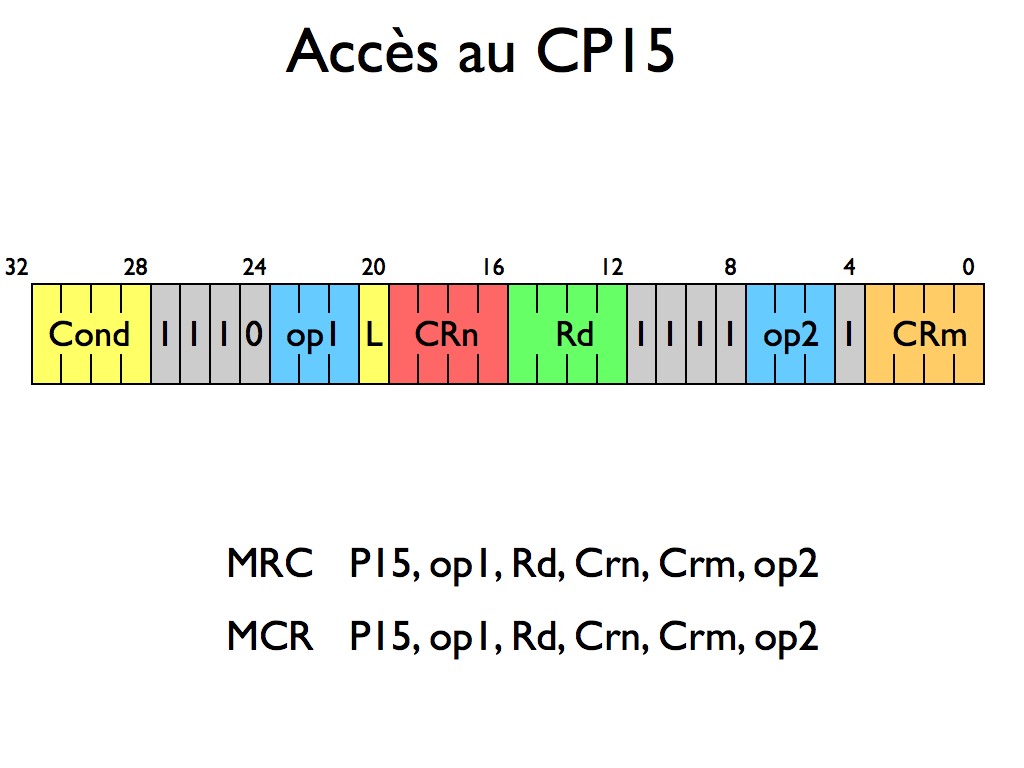

Accès à un co-processeur

Opérations sur les coprocesseurs

Mémoire¶

Accès à la mémoire¶

lecture et écriture mémoire

pseudo instructions d’accès mémoire

transfert de donnée, base plus offset

transfert de donnée, pre-indexation, caractère “!”

transfert de donnée, post-indexation

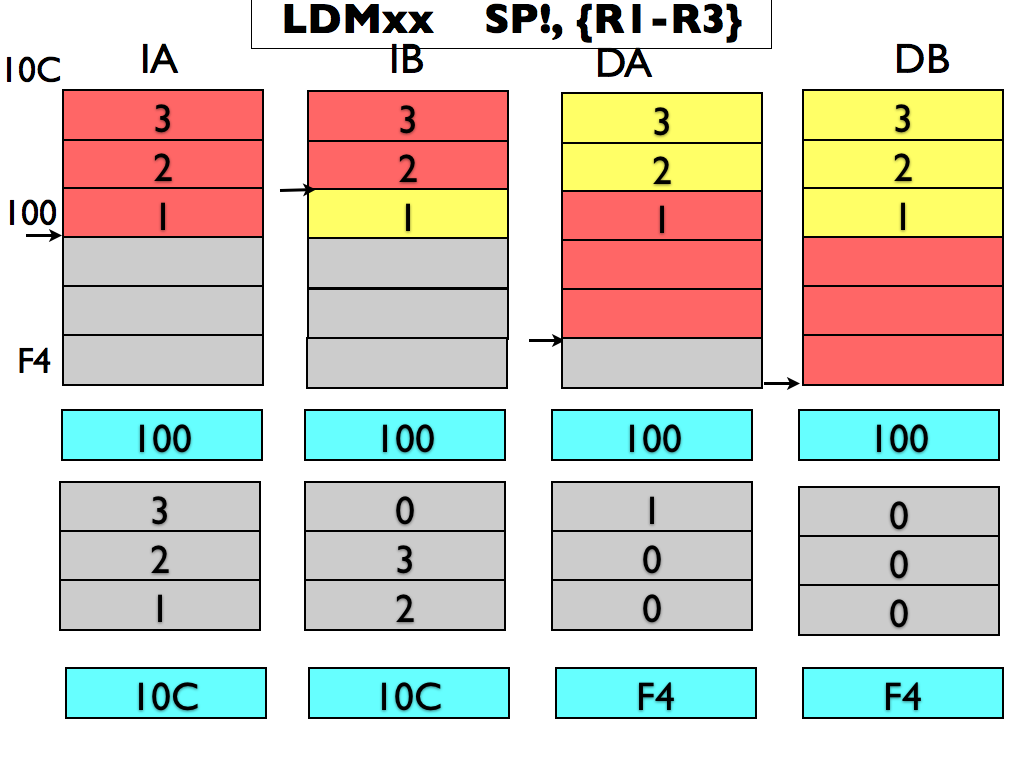

Les accès multiples à la mémoire¶

Accès multiple avec incrément

LDMxx

STMxx

La gestion des piles

Acces multiples et registres cachés

Nouvelles instructions de gestion de modes

Environnement de compilation¶

Programmation C et assembleur¶

Les pointeurs et les tableaux

tests de condition, if et switch

Tableau de fonction

Environnement Linux¶

Le format ELF

ELF

objdump

objcopy

Makefile

script du linker

Directives de l’assembleur GNU¶

Directives de contrôle de flux

Directives de contrôle d’adresse et du loader

Directives de définition de données

Opérations particulières¶

Les opérations atomiques¶

Opérations atomiques ARMv5

Cortex, Exclusive load and store

Bit Banding

Memory Barrier

Mode THUMB¶

Mode THUMB

Changement de mode

Branchement dans THUMB

Instructions THUMB de gestion de données

Instructions d’accès mémoire

THUMB-2, Jazelle, et Jazelle-RCT

Interface C et assembleur ARM¶

Assembleur vers C¶

APCS: ARM Procedure Call Standard

Passage des paramètres

Exemple d’appel de fonction C

Exemple: start_kernel

C vers assembleur¶

Stack frame

Bibliothèques de fonctions assembleur.

Standard C et ARM

GCC assembler inline

Gestion des exceptions¶

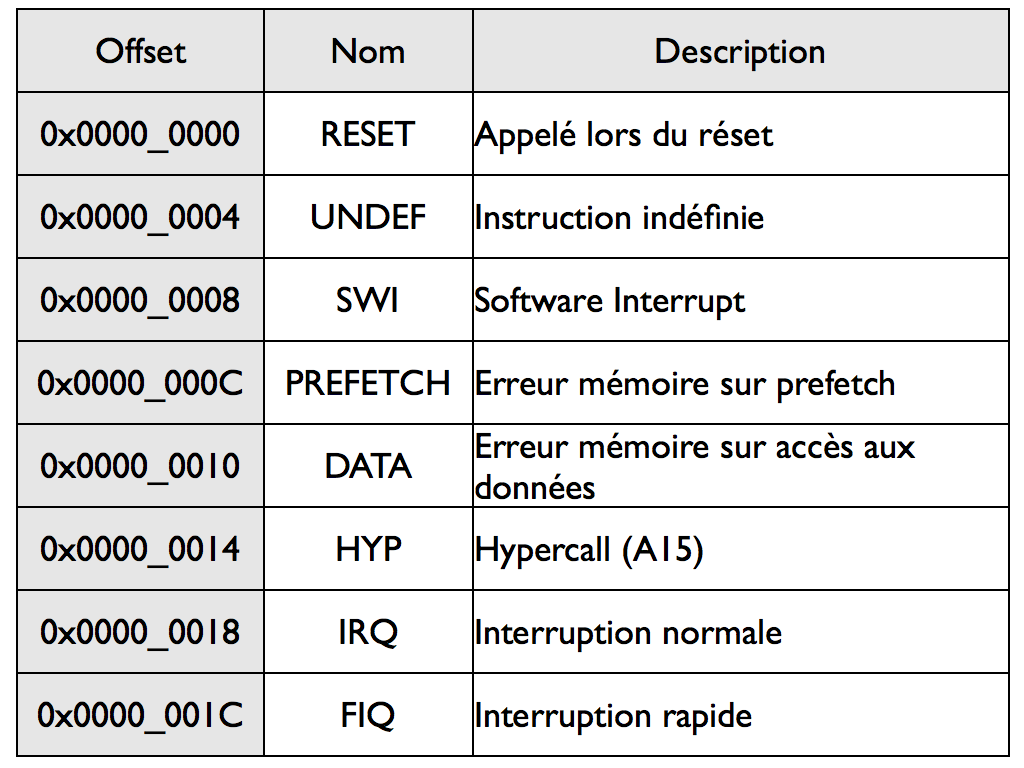

Les vecteurs d’exception¶

Les vecteurs

Adresse des vecteurs

Initialisation des vecteurs d’exception

Exception et pipeline

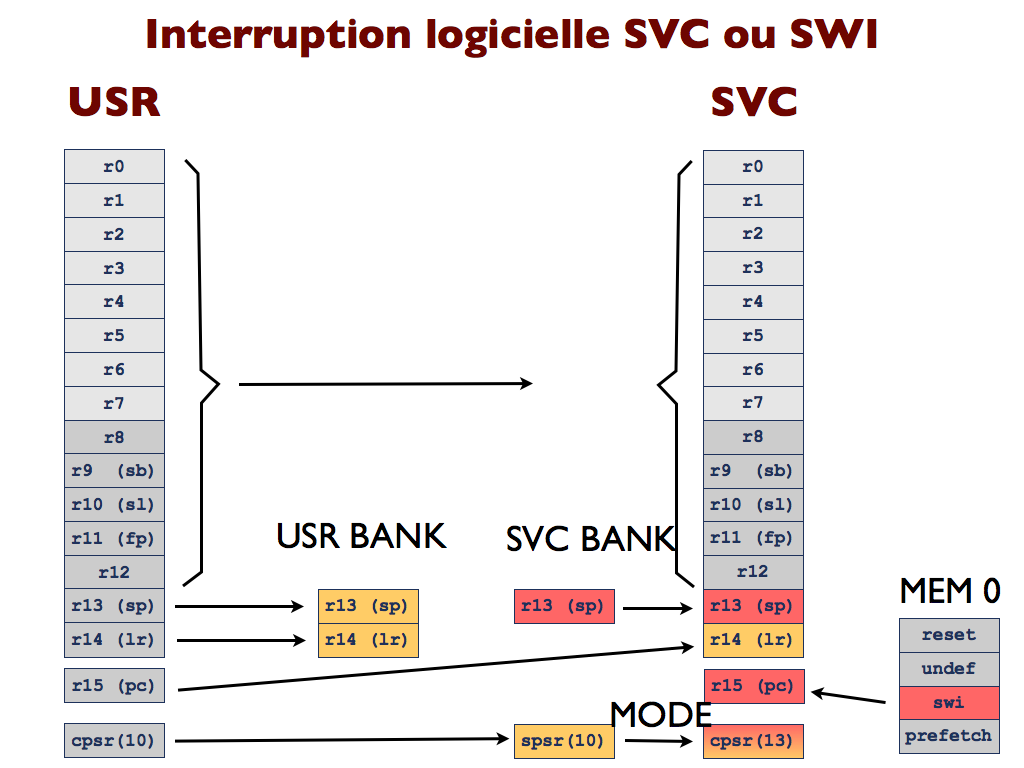

Interruption logicielle

Utilisation des bancs de registres

Retour vers le mode utilisateur

Interruption Matériel IRQ

Interruption Matériel FIQ

Exceptions

Les différentes façons de gérer une interruption¶

Le contrôleur d’interruption

Gestion des IT par ARM

Gestion des interruptions

Gestion standard

Gestion ré-entrante

Gestion de priorité sur les interruptions

Vecteurs incorporés

Présentation de quelques périphériques standards, PIC, timer, UART.

Le dual timer SP-804

Programmation système ARM9¶

gestion des coprocesseurs¶

Différents coprocesseurs

Debug

Coprocesseurs mathématiques

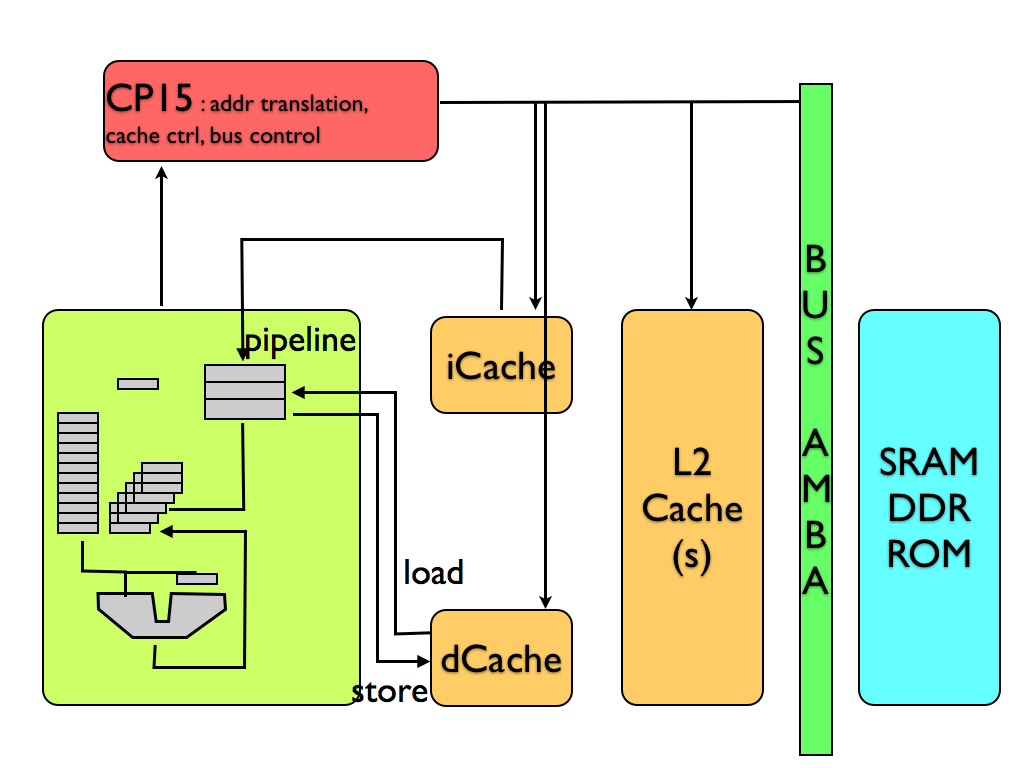

Le coprocesseur système CP15¶

Accès au coprocesseur CP15

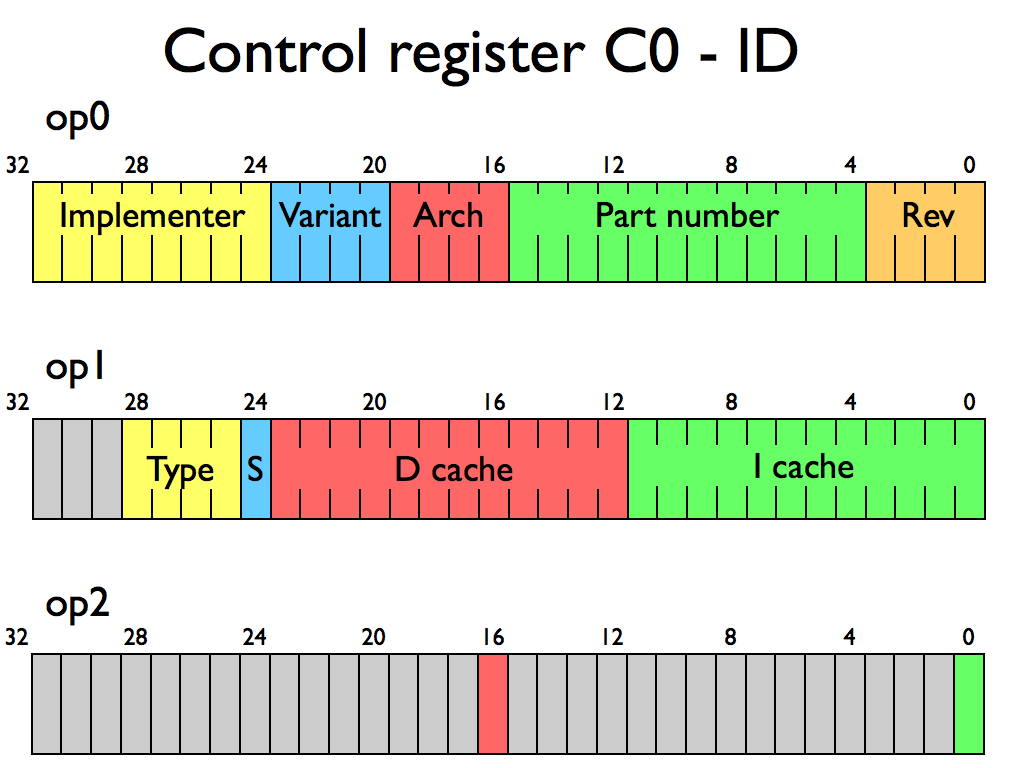

C0: identification

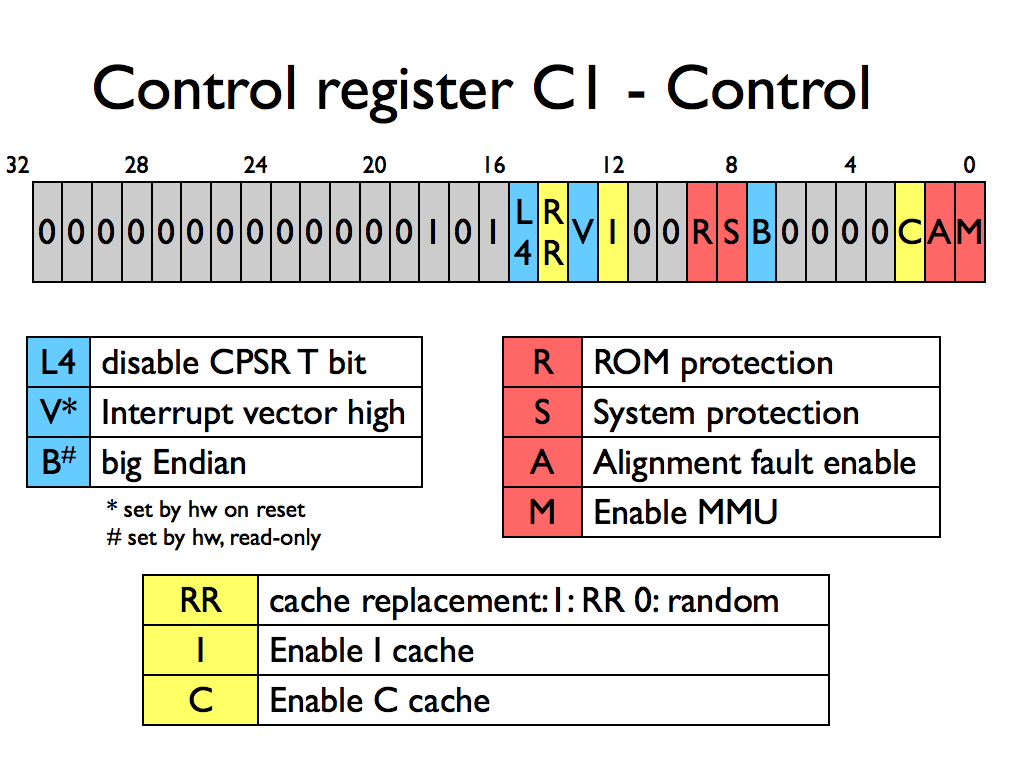

C1: Le registre de contrôle

C2/C3/C8/C10: gestion de la MMU¶

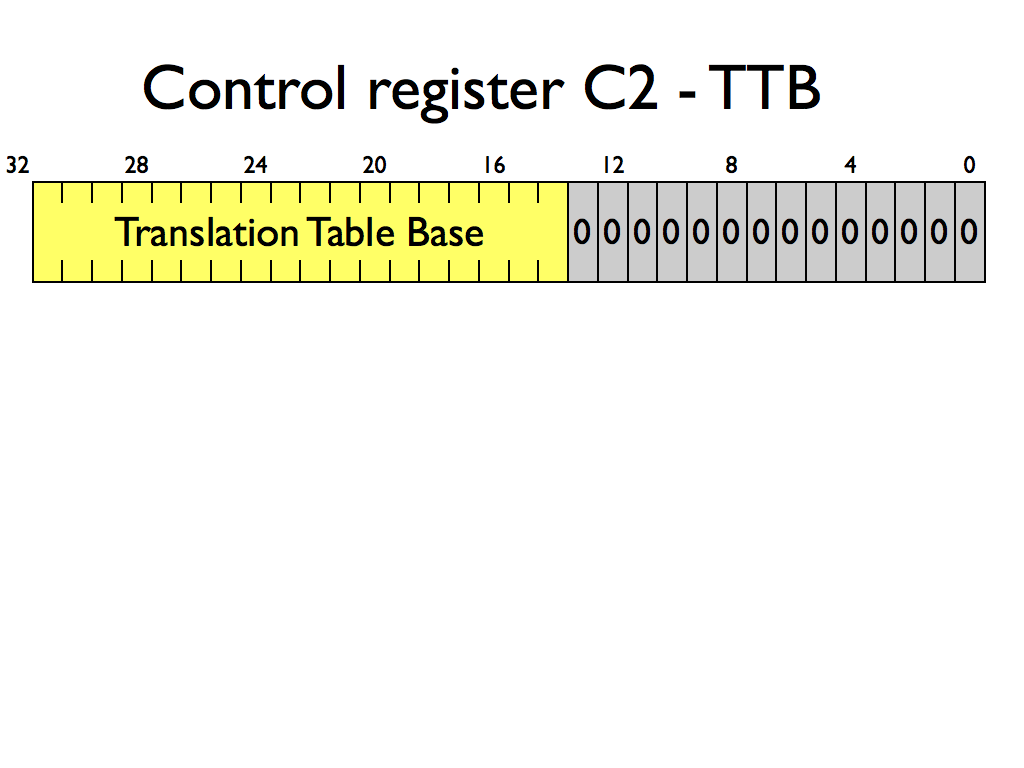

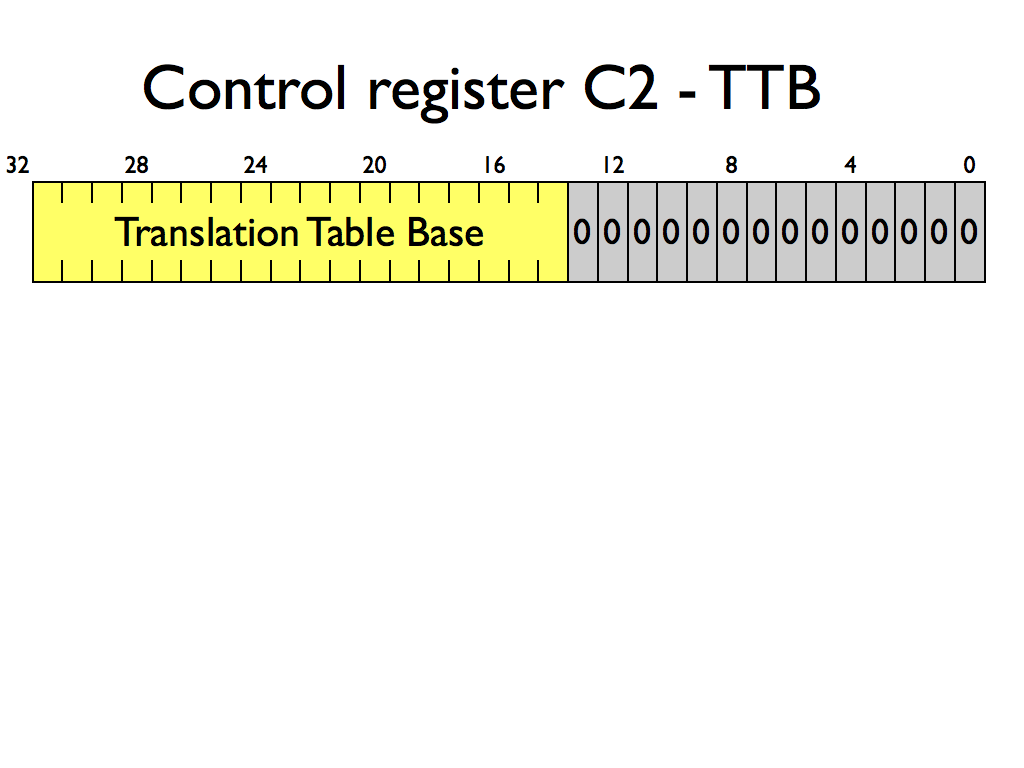

C2 et translation d’adresse

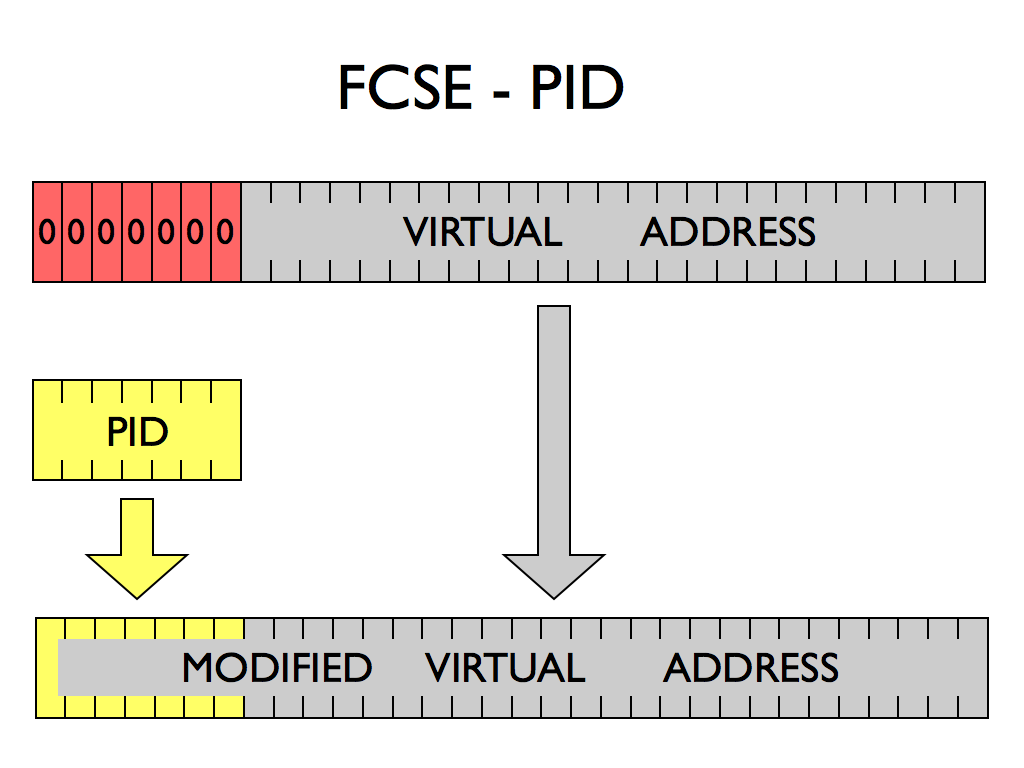

C13: Fast Context Switch Extension

Pagination

rappel de fonctionnement d’une MMU

C8/C10 et changement de contexte et TLB

C2 le registre de contrôle de la MMU

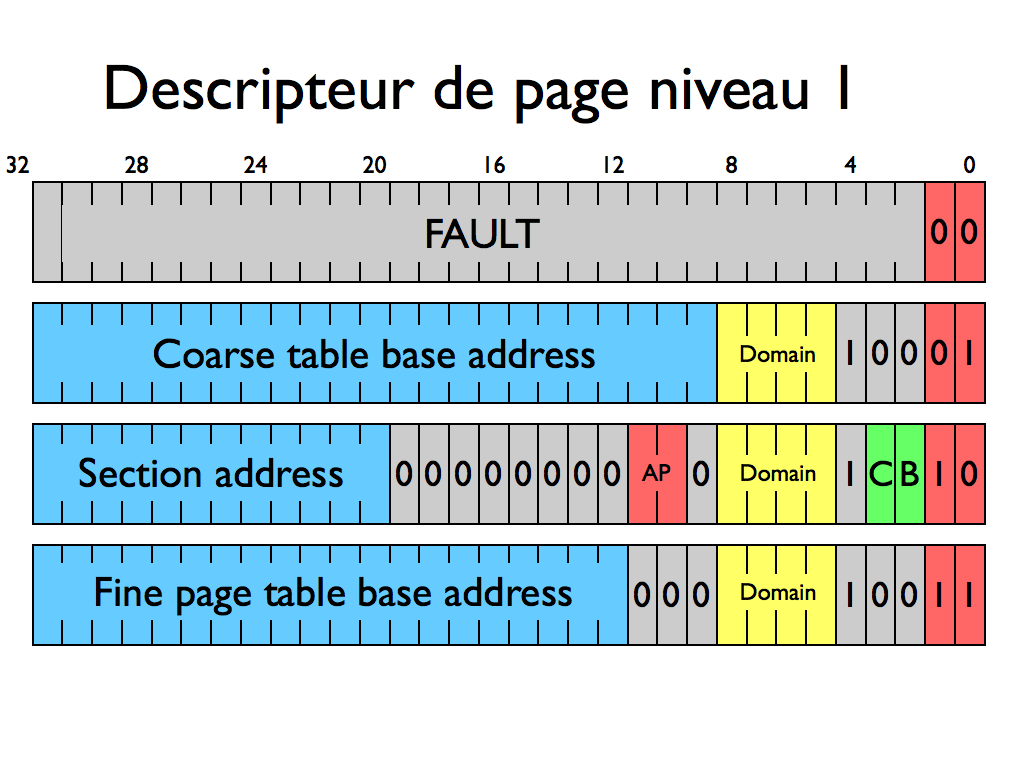

Descripteur de page de niveau 1

Descripteur de section

Descripteurs de niveau I

Les descripteurs de niveau II

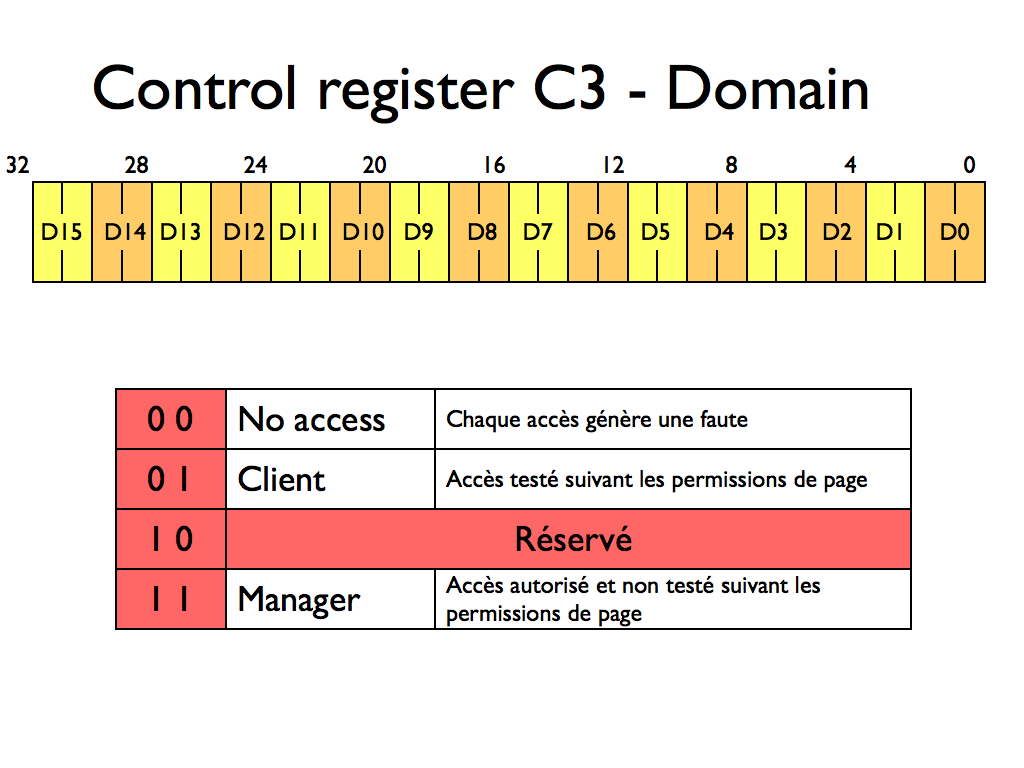

C3: Gestion des domaines

C7: Gestion des cache¶

Caches: ways, index et tags

Incohérence de cache

Coloration de page

C7: La gestion spécifiques des barrières¶

IMB: Instruction Memory Barrier

Barrière d’accès aux données

Rappel sur les barrières

Accès arbitré

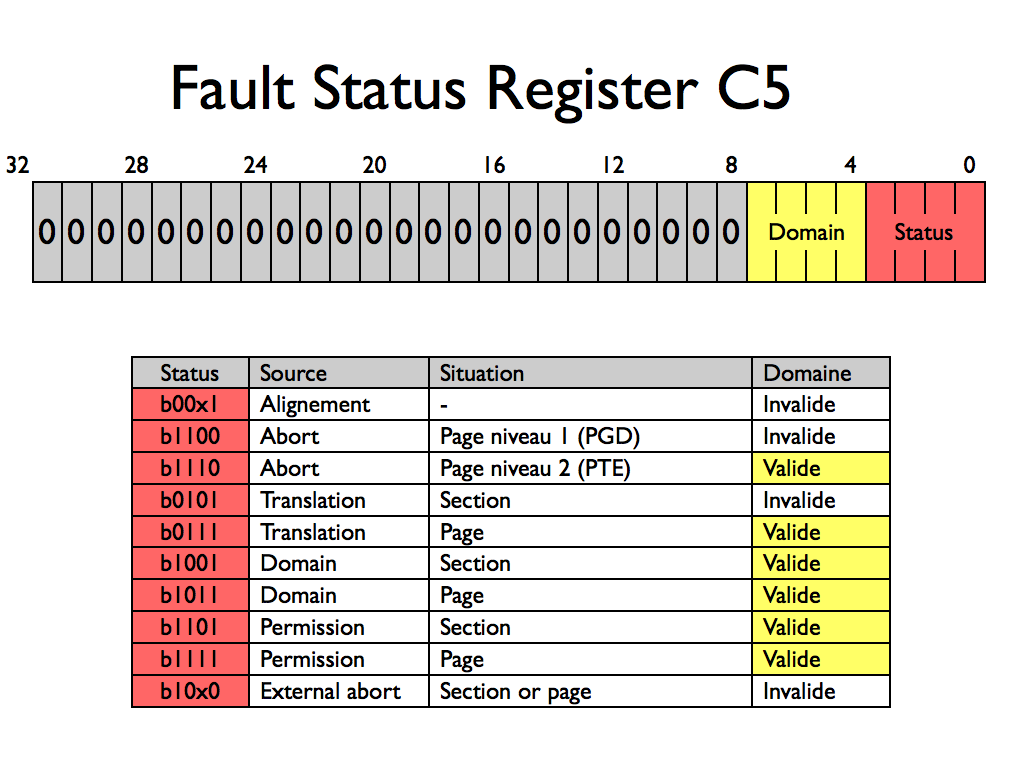

C5/C6: Gestion des fautes¶

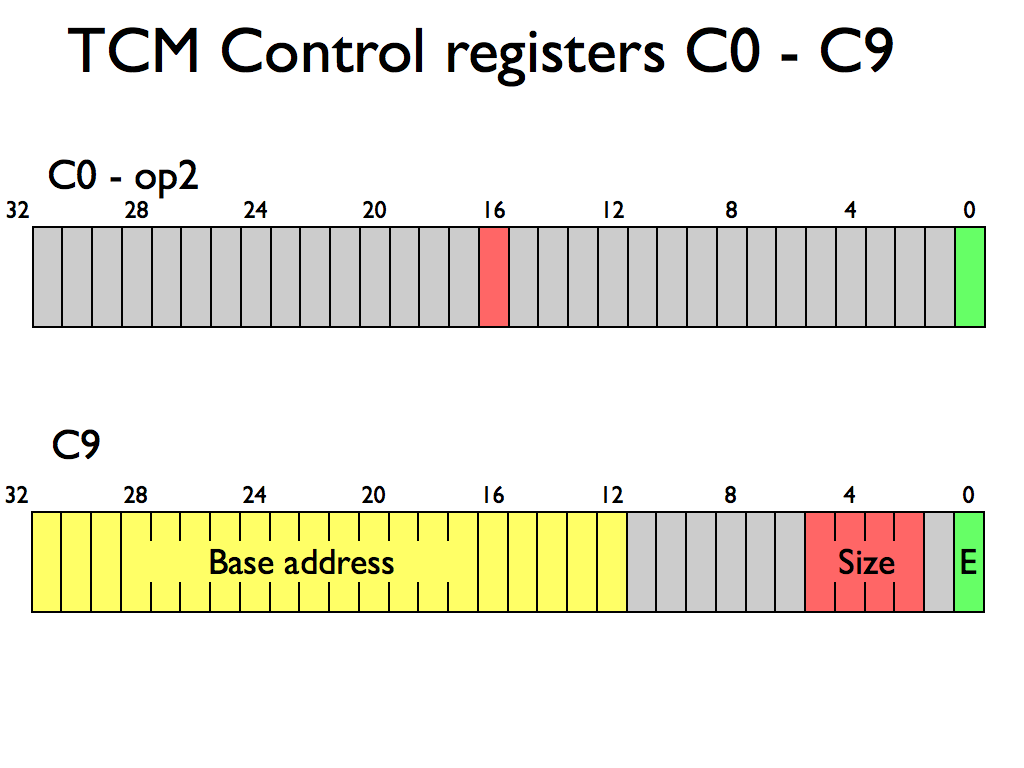

C0/C9: Tiny Coupled Memory¶

Déterminer si la TCM est présente

Accéder à la TCM

Exemple d’utilisation de la TCM

Programmation système Cortex¶

Cortex M¶

Caractéristiques Cortex-M

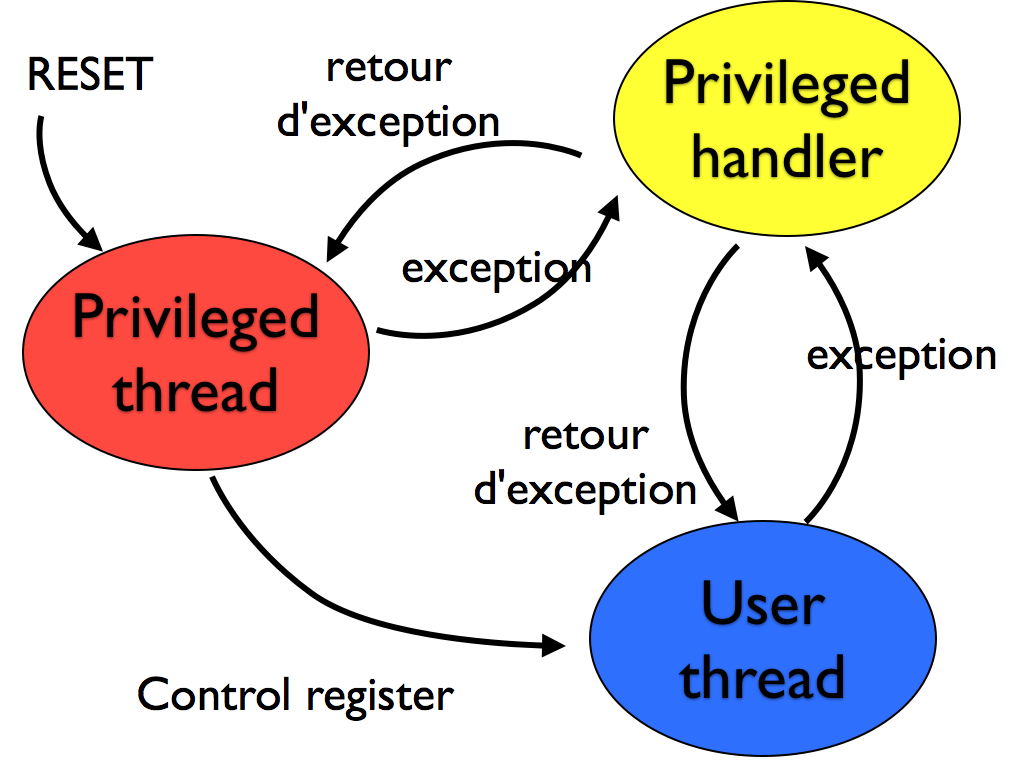

Programmation système Cortex-M3

Nested Vectored Interrupt Support

Gestion mémoire

Code et instructions

Gestion des interruptions et traps

Support de DEBUG

Gestion de pile

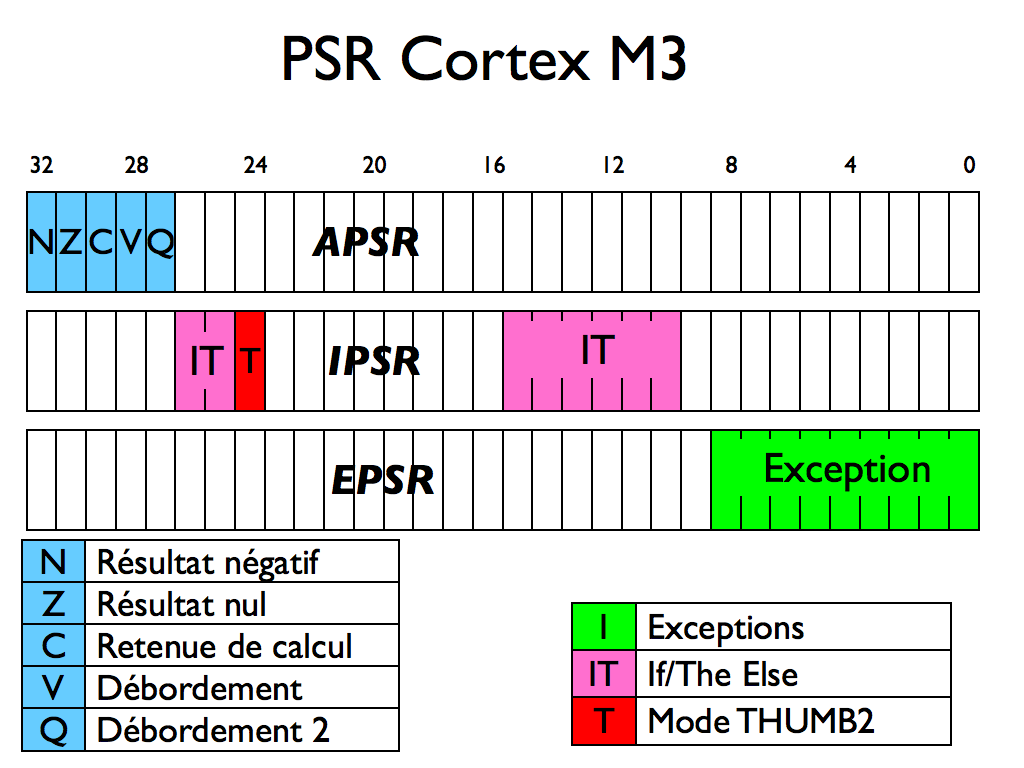

Registres de status

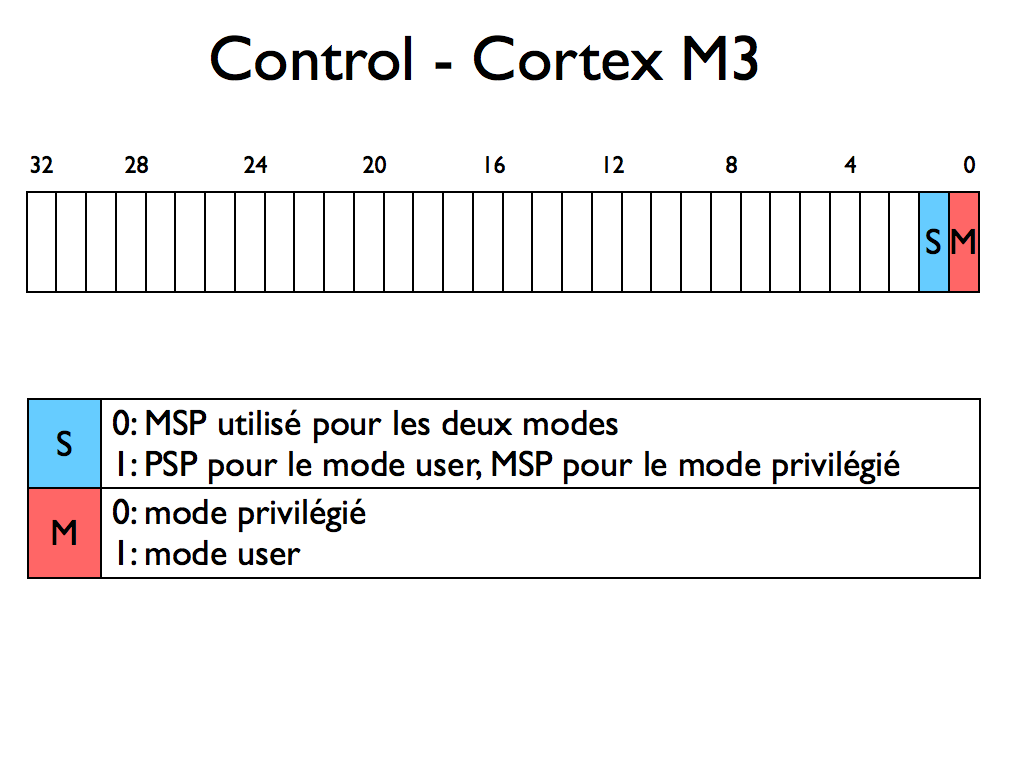

Registre de contrôle

Instruction IT

Instruction CBZ

Memory Barriers

Table Branch

Thumb¶

Mixer THUMB et THUMB2

Mise en œuvre thumb

Le code généré

Utiliser un processeur M3 avec du C uniquement¶

Cortex A¶

Cortex A8

Cortex A9

Cortex A15

big-LITTLE

big.LITTLE task switch

Cluster scheduling

In Kernel Switcher scheduling

HMP Heterogeneous Multi-processing

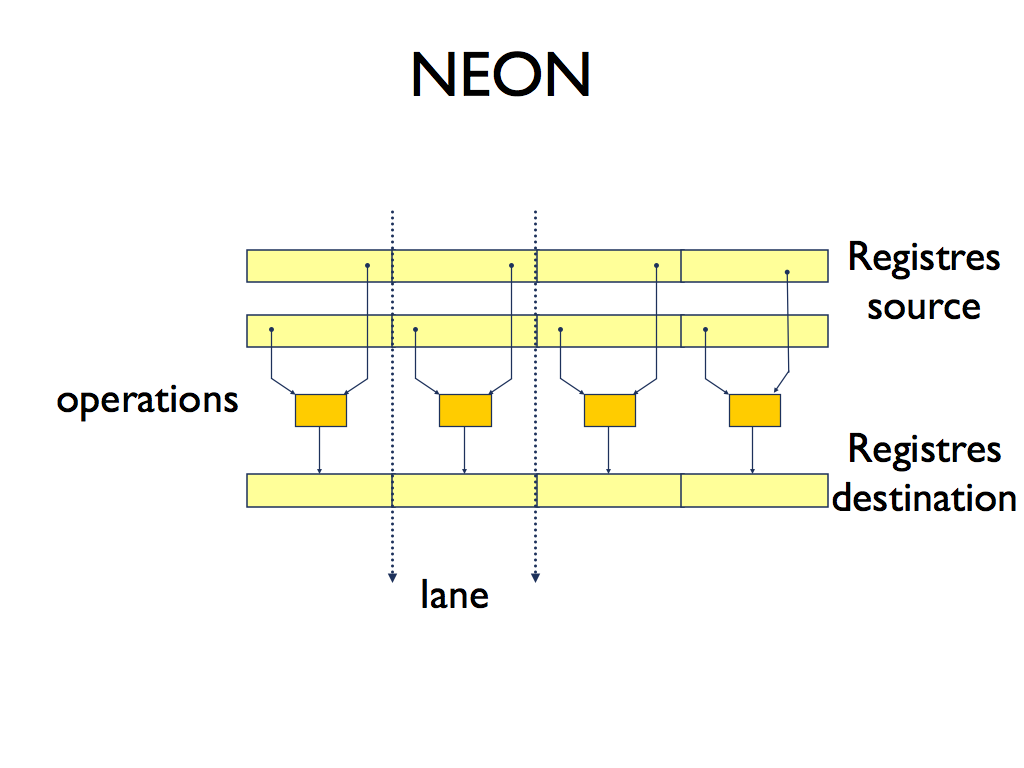

NEON

SMP

Registres spécifique

Wait for interrupt or event

Memory model

ARMv7 accès exclusifs

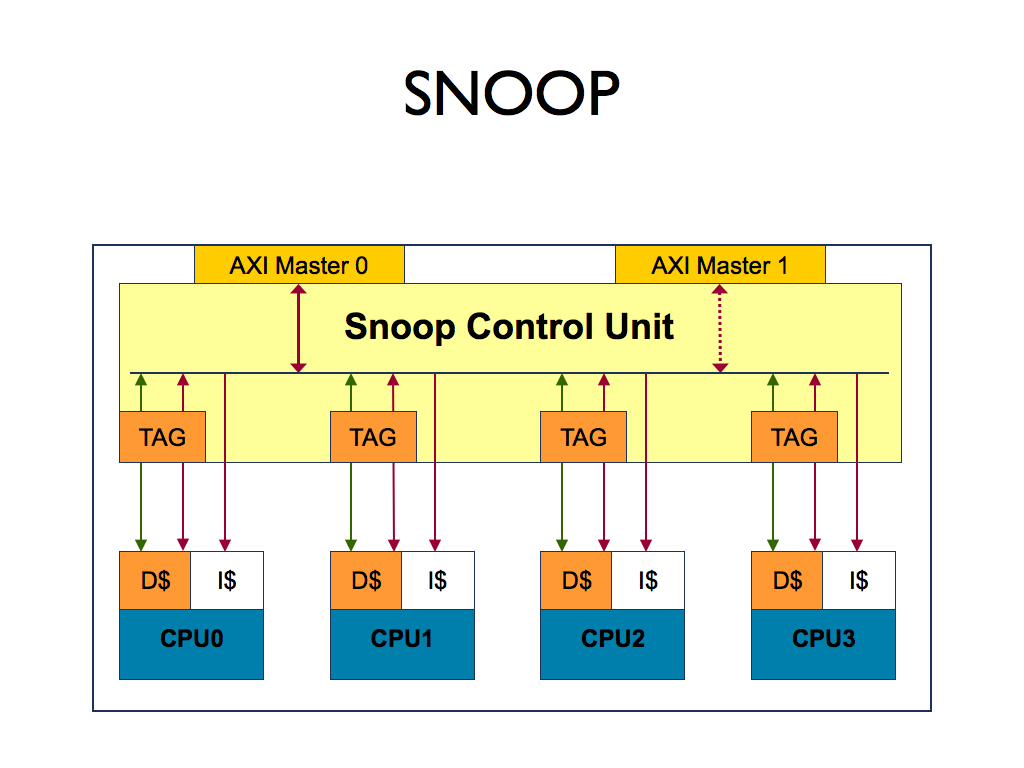

SNOOP Control Unit

Cortex A et Securité¶

Descripteurs de page

Address Space ID

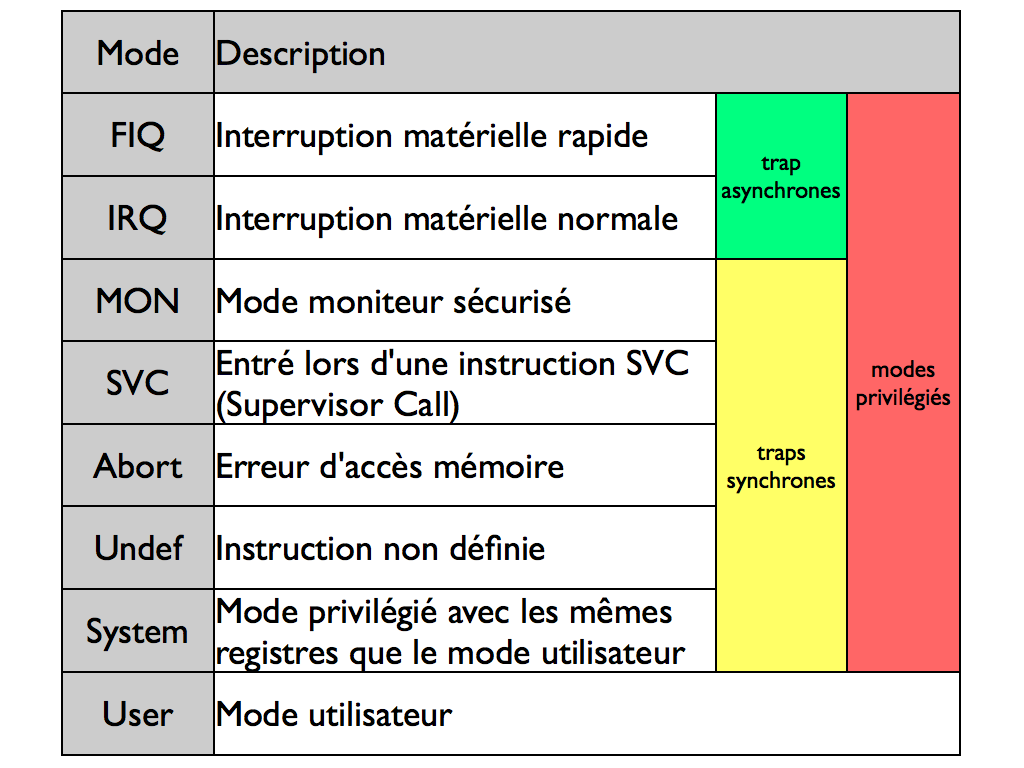

Modes de fonctionnement

Registre CPSR du cortex A8

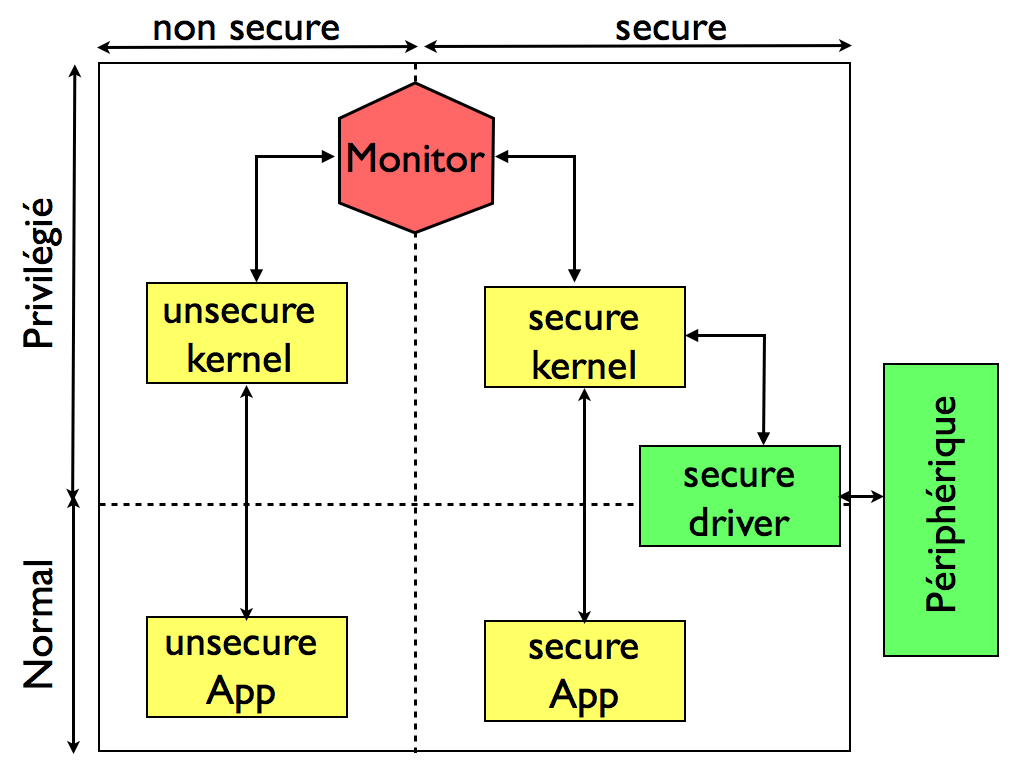

Trustzone¶

Mode secure et non-secure

Conséquences matérielles

boot en mode secure

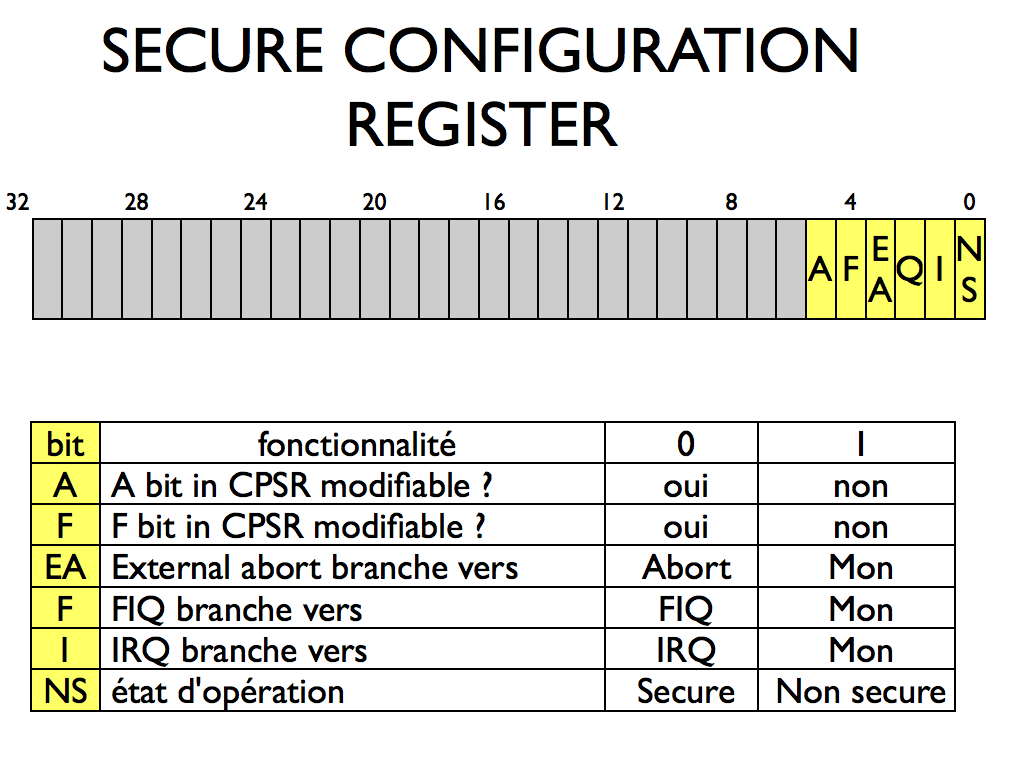

Secure Configuration register

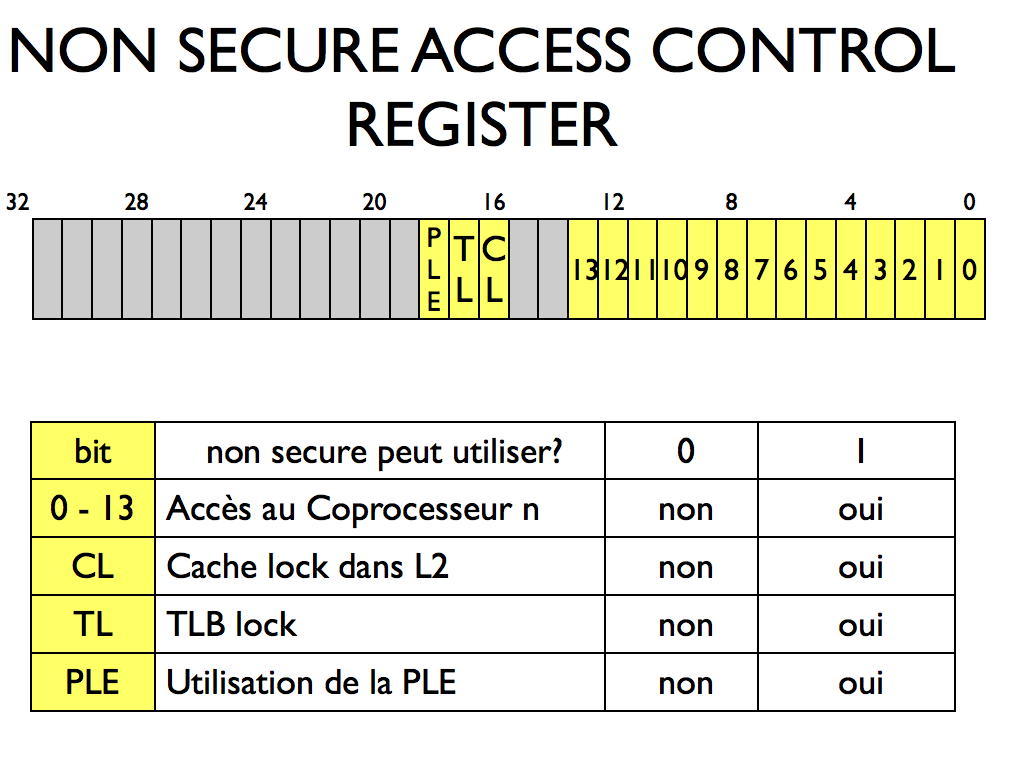

Accès aux coprocesseurs

MMU et accès sécurisé

Les vecteurs

Interruptions

NMI pour mode secure

aspect matériel

Cortex A et virtualisation¶

Virtualisation des interruptions

Virtualisation mémoire